- 259 高校采购信息

- 685 科技成果项目

- 12 创新创业项目

- 0 高校项目需求

语音识别集成电路 IP 与协处理器

1 成果简介

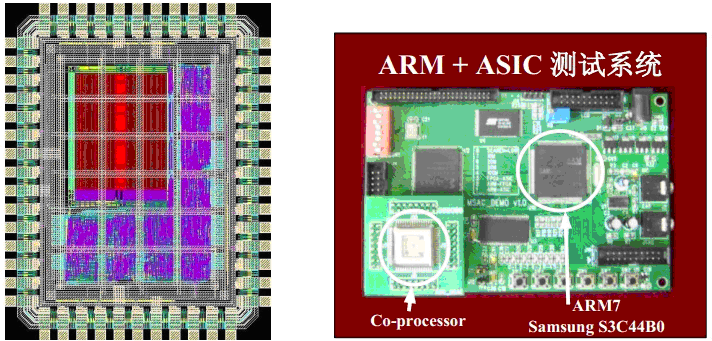

语音识别在嵌入式芯片上实现的主要矛盾是算法实现的性能精度与芯片功耗、速度之间的矛盾,一个性能较好的 800 条典型汉语普通话语音识别算法以纯粹软件嵌入方案实现通常需要 200MIPS 以上 ARM( Advanced Risc Machine) MCU 处理速度,因此我们提出语音识别集成电路 IP 与协处理器来克服以上的问题,通过关键运算的硬件化映射来大幅提高语音识别计算的功耗和处理速度。该设计可作为语音识别集成电路 IP 放入客户的 SoC 芯片中,也可作为协处理器放在片外。 关键性能指标如下: *工艺:苏州 HJTC 0.18um 1P6M 标准 CMOS 工艺 *管芯面积: 1.5 x 2mm *逻辑规模: 3 万等效门(标准二输入与非门,不含 SRAM) *I/O 数: 52 封装: CQFP64 *存储规模:片上集成 1 片单口 SRAM,共 4K×16 比特 *供电电压:核心部分->1.8V, IO 部分->3.3V *正常工作频率: 20MHz(最高工作频率 100MHz) *功耗: 80uW/MHz *速度: 4us/帧(特征维数取 27,时钟频率取 20MHz) 图 1 语音识别集成电路版图图 2 ARM+语音识别协处理的测试系统

表 1 与其他语音识别芯片的对比

2 应用说明

语音识别 IP 或协处理器基于对高斯混合模型计算的优化,适合于各种 HMM 模型的模式识别计算,在语音识别、说话人识别、说话人确认、语音合成等方面均可以广泛应用。 语音识别 IP 或协处理器以加速 ASIC 的模式工作,相同时钟主频下计算性能是 TI C54x系列 16bit DSP 的 5.5 倍以上,对主系统计算性能提升可以达到 4~8 倍。 语音识别 IP 或协处理器对于性能要求型场合和功耗限制型场合都十分适合,芯片支持16bit 并行总线接口,适合于各种 32 位/16 位 MCU 系统,迅速为系统集成高性能语音处理能力。

3 应用范围

- 车载导航, GPS 手机,支持大规模识别词表(例如万条以上的地名)支持模糊语音检索;

- 低端手机平台,支持语音拨号、语音控制,支持用户身份确认、声纹密码。

4 效益分析

语音识别 IP 或协处理器芯片可应用拓展到个人移动信息终端的全市场空间,以 GPS 产品为例,细分的预装 GPS、个人导航设备( Portable Navigation Device, PND), GPS 手机三种产品,根据 CCID( Consulting China Research Center)咨询公司预测 2008 年这三者分别约占到全球市场总量的 15%、 35%和 50%。快速增长的 GPS 市场,对语音识别功能有着非常迫切而又实际的需求, GPS 应用提出的超大规模词表、高混淆度和高环境复杂度这一系列语音识别的技术难题,也只能由语音识别芯片解决。语音识别加快了人机交互与地名等信息的检索,可提高驾驶期间操作 GPS 的行车安全性,同时可以反过来进一步促进 GPS 产品的销售增长。 语音识别技术通过芯片在性能得到大幅提升后,将摆脱传统的人名拨号功能,可用于菜单控制、地名、信息、多媒体内容的检索等等。而语音识别芯片使得低功耗和低成本的要求得以满足,有望成为手机人机交互界面( Man-Machine Interface, MMI)发展的新技术增长点,移动通信领域的市场潜力特别巨大。

扫码关注,查看更多科技成果