- 74 高校采购信息

- 3294 科技成果项目

- 0 创新创业项目

- 0 高校项目需求

智能机器人视觉识别芯片

在信息时代,机器视觉在实现智能社会方面发挥着重要作用。视觉特征提取是机器视觉的一项关键技术,该技术可以提取图像中具有鲜明特征的信息,诸如边缘、角点、圆以及图像形状等特征,这些特征是标定机器视觉系统模型参数和运用机器视觉技术进行实际应用的前提和基础。视觉特征提取技术广泛应用于自主移动智能机器人、无人驾驶和无人机等场景,这些应用场景对视觉特征提取算法的鲁棒性和帧率提出了巨大挑战。

具体来说,视觉特征提取算法包括SIFT(Scale-Invariant Feature Transform,尺度不变特征转换算法)、SURF(Speeded-Up Robust Features,加速稳健特征)、ORB(Oriented FAST and Rotated BRIEF,快速特征点提取描述)、HOG(Histogram of Oriented Gradient,方向梯度直方图)、LBP(Local Binary Patterns,局部二值模式)等。在SURF、ORB、HOG、LBP这些经典的特征提取算法中,SURF的鲁棒性相对较高,但是过于依赖主方向的选取,使得其方向变化鲁棒性不足。SIFT算法可以从图像中提取具有不变性的鲁棒局部特征,对方向变化、光照变化、噪声、杂物场景及遮挡影响等方面的鲁棒性最强,满足无人驾驶技术的需求。SIFT算法的运算量大从而导致的系统帧率低、功耗高的问题可以通过设计具有高并行度的专用硬件加速器芯片来解决。

视觉特征提取技术广泛应用于自主移动智能机器人、无人驾驶和无人机等场景。

基于其初步研究成果,团队已与黑芝麻科技等自动驾驶头部企业合作,联合承担了武汉市科技重大专项“卡脖子”技术攻关项目,研究高鲁棒性、高能效视觉目标识别引擎电路技术,进行车规级高性能自动驾驶芯片设计关键技术的科技攻关。

国内外已有多个SIFT硬件加速器设计发表,总体的研究方向朝着更高性能、更高帧率、更高匹配精度以及更低功耗、更低运算量、更低硬件开销的方向发展。但是对于高性能SIFT硬件加速器的设计仍存在如下三个共性问题和设计挑战:

1.SIFT运算量大,需全并行、全流水架构进行加速,但并行高斯金字塔构建带来了大量的硬件开销;

2.高斯金字塔构建中部分特征点的丢失,使得加速器提取的特征鲁棒性变差;

3.关键点检测部分和描述符生成部分的内部串行执行,两个部分交互执行的方式使得加速器处理速度存在瓶颈,造成系统帧率受限。

图1 高性能SIFT硬件加速器的设计存在的三个共性问题和设计挑战

【解决方案】

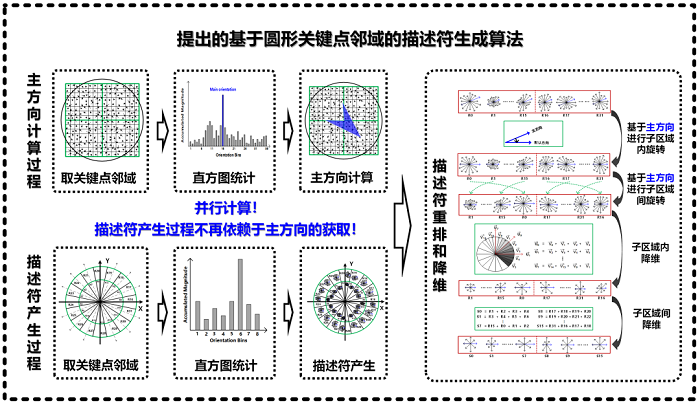

针对上述问题,本成果提出了一系列新方法和新策略,实现了全并行的高能效SIFT硬件加速器芯片硬件架构。针对高斯金字塔构建硬件开销大的问题,提出了快慢双时钟域和部分复用策略;针对高斯金字塔构建过程中的特点丢失问题,提出了动态padding设计策略;针对交互执行及串行计算限制加速性能的问题,提出了一系列并行化的设计方案,即基于乒乓缓存实现了关键点检测和描述符生成部分的并行处理,基于像素梯度预计算实现了关键点检测和梯度幅值辅角的并行计算、以及创新性地提出了一种基于圆形关键点邻域的描述符生成算法,实现了主方向和描述符产生的高效并行计算。

图2 高性能SIFT硬件加速器的设计存在的三个共性问题和对应的设计策略及设计实现

图3 提出的基于圆形关键点邻域的描述符生成算法,可以实现主方向计算和描述符产生过程的并行化计算

【性能指标】

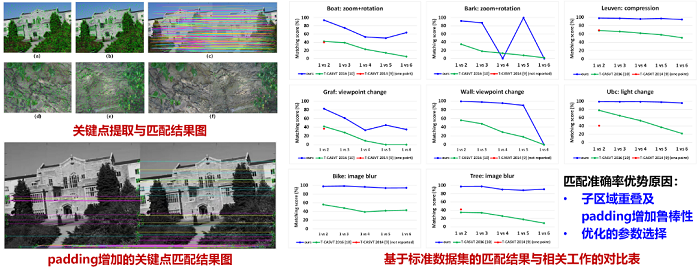

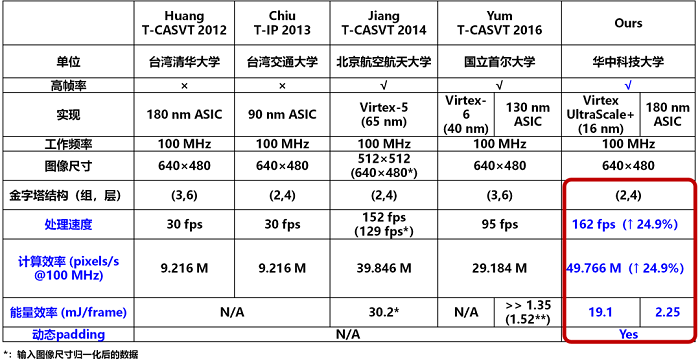

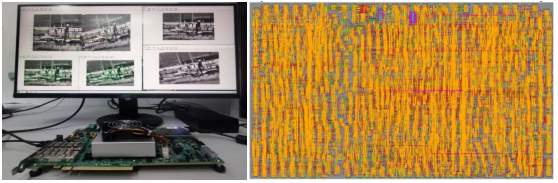

本成果研发的全并行高能效SIFT硬件加速器芯片已在Xilinx Virtex UltraScale+评估板中实现。基于Mikolajczyk and Schmid标准数据集对提出的SIFT设计进行验证,基于RANSAC(RANdom SAmple Consensus)算法检查匹配点的正确性。所提SIFT设计的匹配结果优于相关工作,这主要得益于子区域重叠及padding增加鲁棒性,及优化的参数选择(如高斯卷积核尺寸、关键点邻域大小等)。与文献中相关FPGA及ASIC工作的硬件开销对比显示:该设计的硬件开销总体和现有水平相当,但通过实现了动态padding提高了鲁棒性,同时实现了100 MHz时钟下162 fps VGA的最高帧率和49.766 M pixels/s的最高计算效率。该SIFT硬件加速器在基于180 nm CMOS工艺下实现了2.25 mJ/frame的能量效率。

图4 基于所提SIFT算法的关键点提取与匹配结果图,基于标准数据集的匹配结果与相关工作的比较图

图5 SIFT硬件加速器处理性能比较表:该设计取得了国际SIFT硬件加速器芯片设计中最高帧率的学术记录、最高计算效率和能量效率,并采用了动态padding技术提高了鲁棒性

图6 基于所提出的全并行高能效SIFT硬件加速器芯片的SoC验证平台及65nm芯片版图

扫码关注,查看更多科技成果