高等教育领域数字化综合服务平台

芯片研发技术

围绕自主通用处理器,研发操作系统及其之上的核心 API 软件,支撑国家信息化建设,并致力于构建区别于 Wintel 和 AA 之外的世界第三套信息化生态体系 。

中国科学技术大学

2021-04-14

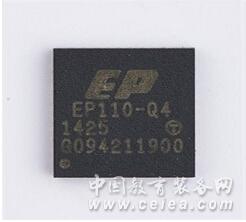

SFP+芯片

产品详细介绍

概述:

1.0625Gbps至4.25Gbps单芯片集成的低功耗SFP+多速率限幅

放大器和VCSEL驱动器高速光收发芯片(EP110)

EP110为高度集成的限幅放大器和VCSEL驱动器,设计用于数据传输速率高达8.5Gbps的1x/2x/4x/8x光纤通道传输系统以及10.3125Gbps数据传输速率的10GBASE-SR传输系统。器件采用+3.3V单电源供电,这款低功耗、集成限幅放大器、VCSEL驱动器和微控制器三合一的高集成单芯片。平均光功率由平均功率控制环路(APC)控制,该控制环路通过连接至VCSEL驱动器的3线数字接口控制、所有差分I/O为50欧姆传输线PCB设计提供最佳的背板短接。EP110集成一个微处理器,可以实现SFF8472协议的数字监控接口要求,可通过固件实现高级Rx设置(模式选择、LOS门限、LOS极性、CML输出电平、信号通道极性)和Tx设置(调制电流、偏置电流、极性、眼图交叉点调制),无需外部微处理器和外部元件。

EP110采用无铅、5mm*5mm、40引脚QFN封装。

1.0625Gbps至10.32Gbps单芯片集成的低功耗SFP+多速率限幅

放大器和VCSEL驱动器高速光收发芯片(EP112)

EP112为高度集成的限幅放大器和VCSEL驱动器,设计用于数据传输速率高达8.5Gbps的1x/2x/4x/8x光纤通道传输系统以及10.3125Gbps数据传输速率的10GBASE-SR传输系统。器件采用+3.3V单电源供电,这款低功耗、集成限幅放大器、VCSEL驱动器和微控制器三合一的高集成单芯片。平均光功率由平均功率控制环路(APC)控制,该控制环路通过连接至VCSEL驱动器的3线数字接口控制、所有差分I/O为50欧姆传输线PCB设计提供最佳的背板短接。EP112集成一个微处理器,可以实现SFF8472协议的数字监控接口要求,可通过固件实现高级Rx设置(模式选择、LOS门限、LOS极性、CML输出电平、信号通道极性)和Tx设置(调制电流、偏置电流、极性、眼图交叉点调制),无需外部微处理器和外部元件。

EP112采用无铅、5mm*5mm、40引脚QFN封装。

1.0625Gbps至14Gbps单芯片集成的低功耗SFP+多速率限幅

放大器和VCSEL驱动器高速光收发芯片(EP116)

EP116是一款低功耗、集成限幅放大器、VCSEL驱动器和微控制器三合一的16G

SFP+高集成高速光收发芯片,工作在高达14Gbps的数据速率、非常适合以太网和光纤通道应用。在EP116的发射和接收路径上集成了CDR功能,解决了大多数高速系统存在的信号失真问题。平均光功率由平均功率控制环路(APC)控制,该控制环路通过连接至VCSEL驱动器的3线数字接口控制、所有差分I/O为50欧姆传输线PCB设计提供最佳的背板短接。EP116集成一个微处理器,可以实现SFF8472协议的数字监控接口要求,可通过固件实现高级Rx设置(模式选择、LOS门限、LOS极性、CML输出电平、信号通道极性、去加重)和Tx设置(调制电流、偏置电流、极性、可编程去加重、眼图交叉点调制),无需外部微处理器和外部元件。

EP116采用无铅、6mm*6mm、48引脚QFN封装。

特点:

3.3供电时,功耗仅为500mW

工作速率高达10.32Gbps

10.32Gbps下,具有5mVp-p接收灵敏度

Rx和Tx极性选择

可调节触发LOS报警电平

LOS极性选择

能够向100欧姆差分负载提供高达12mA的调制电流

偏置电流高达19mA

Rx输出可选择去加重

支持SPI EEPROM和IIC EEPROM

可调节调制输出的眼图交叉点

工作温度: -40度 到 90度

武汉芯光云信息技术有限责任公司

2021-08-23

高性能非制冷红外探测器芯片

技术成熟度:技术突破

研发团队以设计制备宽光谱超材料吸收器和像元级集成红外探测器为研究主线,在超薄宽带高吸收原理与策略、材料/器件设计与制备方面取得了突破性进展。围绕器件吸收率低、噪声等效温差(NETD)大、集成兼容性差的难题,提出了无损与损耗型介质结合、多模谐振耦合光吸收的思路,获得超薄宽带高吸收率材料;提出将超薄宽带高吸收率材料与非制冷红外探测器像元级集成新思路,获得了宽谱、NETD小、多色探测的非制冷红外探测器,NETD降低3倍,研究成果已在中国兵器北方夜视广微科技应用转化。

意向开展成果转化的前提条件:中试放大及产业化工艺开发资金支持

东北师范大学

2025-05-16

基于FPGA的电路板光板测试机

研发阶段/n内容简介:本测试机采用基于现场可编程门阵列(FPGA)和PC104嵌人式工业控制计算机的架构。以PC104为主机,以FPGA及其相应的电路为从机。上位机采用基于Windows的系统软件开发。将测试速度相关的测试控制逻辑、基本测试算法全部移植于FPGA中,从硬件上提高测试机系统速度。将实时性要求不高的人机界面、测试数据处理、上层测试算法及规划由上位机PC104完成。由于测试硬件电路的控制不是由PC104完成,可在不影响系统测试速度下进行复杂测试算法处理,实现测试与数据处理并行操作,提高系统

湖北工业大学

2021-01-12

基于FPGA的电路板光板测试机

研发阶段/n内容简介:本测试机采用基于现场可编程门阵列(FPGA)和PC104嵌人式工业控制计算机的架构。以PC104为主机,以FPGA及其相应的电路为从机。上位机采用基于Windows的系统软件开发。将测试速度相关的测试控制逻辑、基本测试算法全部移植于FPGA中,从硬件上提高测试机系统速度。将实时性要求不高的人机界面、测试数据处理、上层测试算法及规划由上位机PC104完成。由于测试硬件电路的控制不是由PC104完成,可在不影响系统测试速度下进行复杂测试算法处理,实现测试与数据处理并行操作,提高系统

湖北工业大学

2021-01-12

基于 FPGA 的数字信号发生器

本实用新型涉及电子技术领域,具体涉及基于 FPGA 的数字信号发生器,包括 FPGA,D/A 转换器, 外部运算放大器,低通滤波器,功率放大器,键盘,LCD 显示屏;FPGA 与 D/A 转换器、外部运算放大 器、低通滤波器、功率放大器依次相连;键盘、LCD 显示屏分别与 FPGA 相连。该数字信号发生器实现 了 1kHz~1MHz 正弦信号、AM 信号、100kHz~1MHz 频率范围的 FM 信号、二进制 PSK、ASK、FSK 信 号的产

武汉大学

2021-04-14

一种基于 FPGA 的工业智能相机

本实用新型提供一种工业智能相机,包括成像模块、主控制模块、传输模块、电源模块和存储模块,成像模块包括 CMOS 图像传感器及外围电路,主控制模块为 FPGA 芯片,包括图像采集控制模块、图像预处理模块、图像高级处理模块、传输控制模块和存储控制模块。本实用新型提供的工业智能相机采用 FPGA 芯片实现全部图像处理功能,避免了复杂的 FPGA 与 DSP 的交互设计,充分发挥 FPGA 以硬件电路实现算法的处理速度快、性能稳定等优势,相机的集成度高、整体尺寸小、重量低、功耗少,特别适用于对相机尺寸和图像

华中科技大学

2021-04-14

人体器官芯片

成果介绍人体器官芯片的成功研发将有力推动我国生物医疗用芯片制造技术的发展,建立全新的生命科学实验方法;能够有效减少新药研发等对动物和临床实验的依赖,加速新药研发的流程并减少研发投入技术创新点及参数微缩人工器官,以实现对人体器官功能的模拟。器官芯片高内涵装置的设计和制造,开发了标准芯片系统及器官特异性生物材料市场前景疾病模型,药物评估,个性化医疗。

东南大学

2021-04-13

智能开关芯片

GaN系列材料具有低的热产生率和高击穿电场,是制作大功率电子器件的重要材料。利用GaN材料制造的功率管拥有承受大电流、耐高压、抗辐射,耐高温而且开关速度快的特点,非常适用于高功率微波器件。随着5G毫米波通信、工业4.0和新一代雷达的发展,这种功率微波器件将会得到更广泛的应用。但是,对于这种半导体器件的负载开关驱动提出了非常高的要求。要求负载开关驱动封装尺寸小,便于大阵列集成。并且对可靠行的要求也极高。智能功率集成电路(Smart Power Inte

南京大学

2021-04-14

高性能专用芯片

交流伺服系统是跨行业、量大面广、节能效果显著的节能机电产品,几乎渗透到所有用机电领域,是工业、农业和国防建设及人民生活、正常生产和安全工作的重要保证。

南京大学

2021-04-14